# **Area Flexible GF(2<sup>k</sup>) Elliptic Curve Cryptography Coprocessor**

Adnan Abdul-Aziz Gutub Computer Engineering Department, King Fahd University of Petroleum and Minerals, SA

**Abstract:** Elliptic Curve Cryptography (ECC) is popularly defined either over GF(p) or  $GF(2^k)$ . This research modifies a GF(p) multiplication algorithm to make it applicable for  $GF(2^k)$ . Both algorithms, the GF(p) and  $GF(2^k)$ , are designed in hardware to be compared. The  $GF(2^k)$  multiplier is found to be faster and smaller. This  $GF(2^k)$  multiplier is further improved to benefit in speed, it gained more than 40% faster speed with the cost of 5% more area. This multiplier hardware is furthermore adjusted to have area flexibility feature, which is used as the basic block in modeling a complete projective coordinate  $GF(2^k)$  ECC coprocessor.

**Keywords:** Elliptic curve cryptography, modular multiplication, area flexible multiplier, projective coordinates.

Received May 1, 2005; accepted August 1, 2005

#### 1. Introduction

Cryptography is a well-recognized technique for information protection. It is used effectively to protect sensitive data such as passwords that are stored in a computer, as well as information being transmitted through different communication media. Encryption is the transformation of data into a form, which is very hard to retransform back by anyone without a secret decryption key. Even if someone steals the encrypted information, he cannot benefit from it.

Depending on the encryption/decryption key, crypto-systems can be classified into two main categories: Secret key cryptosystems and public key cryptosystems. The secret key cryptosystems uses one key for both encryption and decryption. Public key cryptosystems, however, use two different keys, one for encryption and the other for decryption. Secret key cryptosystems is used for encryption and decryption of messages, while, public key cryptosystems is used for digital signature and key exchange schemes. Although public key systems can be used for message encryption and decryption, it is found to be very slow. This made it practical to be used for digital signature and key exchange scheme more than encryption and decryption of messages.

In 1985, Koblitz and Miller independently proposed the Elliptic Curve Cryptosystem (ECC) [2, 3, 4, 12, 15, 16, 17, 21, 22,], a method based on the discrete logarithm problem over the points on an elliptic curve. Since that time, ECC has received considerable attention from mathematicians around the world, and no significant breakthroughs have been made in determining weaknesses in the algorithm. Although critics are still skeptical as to the reliability of this method, several encryption techniques have been

developed recently using these properties. The fact that the problem appears so difficult to crack means that key sizes can be reduced in size considerably, even exponentially [15, 17, 21], especially when compared to the key size used by other cryptosystems. This made ECC become a challenge to the RSA, one of the most popular public key methods known. ECC is showing to offer equal security to RSA but with much smaller key size. In addition to their simplicity and smaller size, ECC are more likely to be adopted in the future, especially in systems with limited processing and storage resources such as those incorporating mobile devices and smart cards [21]. This main advantage makes Elliptic Curves (EC) attractive and benefits the possibility of optimizing its arithmetic operations in the underlying field. This has led to the appearance of several elliptic curve cryptography products such as Security Builder, SSL Plus, WTLS Plus, TrustPoint, etc. In addition, many companies have purchased licenses to use EC codes and embed them in their products [1].

In order to use ECC, an elliptic curve must be defined over a specific finite field. Some finite field representations may lead to more implementations than others, in hardware or in software. The EC arithmetic can be optimized depending on the type of finite field. The most popular finite fields used in ECC are Galois Fields, GF(p) and  $GF(2^k)$  [1, 3, 4, 10, 11, 12, 21]. In this research, these two finite fields are compared. The number of arithmetic operations in GF(p) is found to be less than  $GF(2^k)$ , but each operation in GF(p) consumes much more time and area than  $GF(2^k)$ . This made up working with  $GF(2^k)$  seams more efficient than GF(p).

A basic operation in the ECC arithmetic is modular multiplication. This research adjust a GF(p) multiplication algorithm to make it applicable for  $GF(2^k)$ . Both algorithms are modeled in hardware to be compared and analyzed. The  $GF(2^k)$  multiplier hardware is found to be faster and smaller. It is further modified and speeded up with a very small cost of area. The  $GF(2^k)$  multiplier hardware is designed with a re-configurable area dependant way, such that the hardware is area flexible, it can be designed according to what area is available.

The organization of this paper is as follows. Section 2 will give some background on the elliptic curve theory and some efficient implementation study of ECC. In section 3, the GF(p) multiplication algorithm will be modified for  $GF(2^k)$  which made up the basic multiplier hardware. In section 4, a complete ECC coprocessor model is proposed. Section 5 concludes the paper.

# 2. Elliptic Curves and their Implementations

Elliptic curves are known so because they are described by cubic equations, similar to those used in ellipsis calculations. The general form for elliptic curve equation is:  $y^2 + axy + by = x^3 + cx^2 + dx + e$ . There is also a single element named the *point at infinity* or the *zero point* denoted ' $\varphi$ '. The point at infinity is computed as the sum of any three points on an elliptic curve that lie on a straight line. If a point on the elliptic curve is to be added to another point on the curve or to itself, some special addition rules are applied depending on the finite field used. For more details on the elliptic curve theory, the reader is advised to look through [2, 4, 21, 22].

A finite field is a set of elements that have a finite order (number of elements). The order of *Galois Field* (*GF*) is normally a prime number or a power of a prime number. There are many ways of representing the elements of the finite field. Some representations may lead to more efficient implementations of the field arithmetic in hardware or in software. The elliptic curve arithmetic is more or less complex depending on the finite field where the elliptic curve is applied. GF(p) and  $GF(2^k)$  are considered in this research because of their popularity in ECC [1, 3, 4, 7, 8, 9, 11, 12, 21].

The basic element of an elliptic curve cryptosystem is the calculation of the point kP, where kP = P + P... + P (k - times). Designing an efficient ECC hardware coprocessor depends tremendously on the type of finite field used. Most ECC hardware researches [15, 16, 17], show that the ECC implementations defined over  $GF(2^k)$  are more suitable than GF(p), especially when embedded into restricted area, such as smart cards. The simplicity of  $GF(2^k)$  in hardware comes from the possibility of doing arithmetic without carry

propagation. ECC, however, is not restricted to smart cards. There can be some hardware applications where GF(p) can be more appropriate to use than  $GF(2^k)$  [3].

The following subsections are going to compare the elliptic curve point addition in the two finite fields: GF(p) and  $GF(2^k)$ . The comparison is targeted towards finding out if GF(p) can possibly be faster than  $GF(2^k)$ . This study will compare the number of the most-time-consuming operations in both finite fields. The costly arithmetic operations are assumed to be multiplication, inversion (division), and squaring. Addition, subtraction, and multiplication by small constants are not expensive [2, 12], so their cost is neglected.

# 2.1. Comparing GF(p) and GF(2<sup>k</sup>)

The addition of two different points on the elliptic curve is computed as shown in Table 1. The number of operations, as observed, is found to be the same in both fields (neglecting the addition, subtraction, and multiplication of small numbers [2, 12]). Lambda requires one inversion and one multiplication in order to be calculated. Computing  $x_3$  needs only one squaring of lambda. The value of  $y_3$  is figured with one multiplication operation of lambda. The number of operations in both fields is the same: One inversion, one squaring, and two multiplication calculations.

Table 1. Addition of two different points on the elliptic curve.

| $(x_1, y_1) + (x_2, y_2) = (x_3, y_3)$ ; where $x_1 \neq x_2$ |                                             |  |

|---------------------------------------------------------------|---------------------------------------------|--|

| GF(p)                                                         | $GF(2^k)$                                   |  |

| $\lambda = (y_2 - y_1) / (x_2 - x_1)$                         | $\lambda = (y_2 + y_1) / (x_2 + x_1)$       |  |

| $x_3 = \lambda^2 - x_1 - x_2$                                 | $x_3 = \lambda^2 + \lambda + x_1 + x_2 + a$ |  |

| $y_3 = \lambda(x_1 - x_3) - y_1$                              | $y_3 = \lambda(x_1 + x_3) + x_3 + y_1$      |  |

The addition of a point to itself (doubling a point) on the elliptic curve is computed as shown in Table 2. Computing lambda in GF(p) requires an inversion, a multiplication, and a squaring of  $x_I$ , while it needs an inversion and a multiplication in  $GF(2^k)$ . Calculating ' $x_3$ ' in both fields want the same operation of squaring lambda. Computing ' $y_3$ ' in GF(p) requires only one multiplication, while it needs a multiplication and a squaring operations in  $GF(2^k)$ . The number of operations is found to be the same in both fields: An inversion, two squaring, and two multiplication calculations [2, 12].

In point operations of both finite fields GF(p) and  $GF(2^k)$  (adding two points and doubling a point), the number of operations is found to be the same. However, the time required to complete each operation differs much in each field.

Table 2. Doubling a point on the elliptic curve.

| $(x_1, y_1) + (x_1, y_1) = (x_3, y_3)$ ; where $x_1 \neq 0$ |                                     |  |

|-------------------------------------------------------------|-------------------------------------|--|

| GF(p)                                                       | $GF(2^k)$                           |  |

| $\lambda = (3(x_I)^2 + a) / (2y_I)$                         | $\lambda = x_1 + (y_1) / (x_1)$     |  |

| $x_3 = \lambda^2 - 2x_1$                                    | $x_3 = \lambda^2 + \lambda + a$     |  |

| $y_3 = \lambda(x_1 - x_3) - y_1$                            | $y_3 = (x_1)^2 + (\lambda + 1) x_3$ |  |

Crutchley [4] in his master thesis has made a time comparison between GF(p) and  $GF(2^k)$ . His result shows that the multiplication process in GF(p) is the only faster operation than  $GF(2^k)$ . All other operations are reported to be slower in GF(p) than in  $GF(2^k)$ . It seems that his conclusions are generated from a software implementation of the operations. Software arithmetic computations depend on the general purpose processors which is built for GF(p) arithmetic. Therefore, software ECC GF (p) operations is found faster than  $GF(2^k)$ , which made ECC  $GF(2^k)$  software researches [1, 11] proposed modified methods to compute the operations specifically for utilizing the general purpose processors capabilities. Our research here is targeted to design specific ECC hardware. We proved that the normal hardware  $GF(2^k)$  calculations are faster than GF(p), as studied in a following section.

Several hardware design attempts [13, 18, 19] have investigated ECC Field Programmable Gate Array (FPGA) implementations. They focus on the features and capabilities of each specific FPGA used. To increase the FPGA design efficiency, every design is built for a specific finite field order that cannot be utilized for any other order. However, in this work, we propose a general hardware that is for any  $GF(2^k)$  finite field order and flexible in hardware size, it can fit on any area available.

Calculating the inverse is the most expensive operation. Designs replace the inversion by several multiplication operations by representing the elliptic curve points as projective coordinate points [2, 12, 15, 22].

# 2.2. Projective Coordinates in GF(p)

The projective coordinates are used to eliminate the need for performing inversion. For elliptic curve defined over GF(p), two different forms of formulas are found [2, 12] for point addition and doubling. One form projects  $(x, y) = (X / Z^2, Y / Z^3)$  [2], while the second projects (x, y) = (X / Z, Y / Z) [12].

The two forms procedures for projective point addition of P+Q (two elliptic curve points) is shown below:

$$P = (X_1, Y_1, Z_1); Q = (X_2, Y_2, Z_2); P + Q = (X_3, Y_3, Z_3);$$

where  $P \neq \pm Q$

$$(x, y) = (X / Z^2, Y / Z^3) \rightarrow (X, Y, Z) (x, y) = (X / Z, Y / Z) \rightarrow (X, Y, Z).$$

The squaring calculation over GF(p) is very similar to the multiplication computation. They both are noted as M (multiplication). It is worth noting that any EC cryptoprocessor must implement the procedures of projective coordinates efficiently since they are the core steps of the point operation algorithm of ECC.

$$\lambda_1 = X_1 Z_2^2 \qquad 2M \qquad \lambda_1 = X_1 Z_2 \qquad IM$$

Similarly, the two forms of formulas for projective point doubling is shown below:

$$P = (X_{1}, Y_{1}, Z_{1}); P + P = (X_{3}, Y_{3}, Z_{3})$$

$$(x, y) = (X/Z^{2}, Y/Z^{3}) \Rightarrow (X, Y, Z)$$

$$(x, y) = (X/Z, Y/Z) \Rightarrow (X, Y, Z)$$

$$\lambda_{1} = 3X_{1}^{2} + aZ_{1}^{4} \qquad 4M \qquad \lambda_{1} = 3X_{1}^{2} + aZ_{1}^{2} \qquad 2M$$

$$Z_{3} = 2Y_{1}Z_{1} \qquad 1M \qquad \lambda_{2} = Y_{1}Z_{1} \qquad 1M$$

$$\lambda_{2} = 4X_{1}Y_{1}^{2} \qquad 2M \qquad \lambda_{3} = X_{1}Y_{1}\lambda_{2} \qquad 2M$$

$$X_{3} = \lambda_{1}^{2} - 2\lambda_{2} \qquad 1M \qquad \lambda_{4} = \lambda_{1}^{2} - 8\lambda_{3} \qquad 1M$$

$$\lambda_{3} = 8Y_{1}^{4} \qquad 1M \qquad X_{3} = 2\lambda_{4}\lambda_{2} \qquad 1M$$

$$\lambda_{4} = \lambda_{2} - 2X_{3} \qquad Y_{3} = \lambda_{1}(4\lambda_{3} - \lambda_{4}) - 8(Y_{1}\lambda_{2})^{2} \qquad 3M$$

$$Y_{3} = \lambda_{1}\lambda_{4} - \lambda_{3} \qquad 1M \qquad Z_{3} = 8\lambda_{2}^{3} \qquad 2M$$

$$10M \qquad 12M$$

## 2.3. Projective Coordinates in GF(2k)

For elliptic curve defined over  $GF(2^k)$ , to eliminate the need for performing inversion, its coordinates (x, y) are to be projected to (X, Y, Z). Similar in principle to GF(p) projective coordinates, two different forms of formulas are found [2, 6] for point addition and doubling. One form projects  $(x, y) = (X/Z^2, Y/Z^3)$  [2], while the second projects (x, y) = (X/Z, Y/Z) [6].

The two forms procedures for projective point addition of P + Q (two elliptic curve points) is shown below:

$$P = (X_{1}, Y_{1}, Z_{1}); Q = (X_{2}, Y_{2}, Z_{2}); P + Q = (X_{3}, Y_{3}, Z_{3});$$

$$where P \neq \pm Q$$

$$(x, y) = (X/Z^{2}, Y/Z^{3}) \Rightarrow (X, Y, Z)$$

$$(x, y) = (X/Z, Y/Z) \Rightarrow (X, Y, Z)$$

$$A = X_{1}Z_{2}^{2} \qquad 2M \qquad A = X_{1}Z_{2} \qquad IM$$

$$B = X_{2}Z_{1}^{2} \qquad 2M \qquad B = X_{2}Z_{1} \qquad IM$$

$$C = A + B \qquad C = A + B$$

$$D = Y_{1}Z_{2}^{3} \qquad 2M \qquad D = Y_{1}Z_{2} \qquad IM$$

$$E = Y_{2}Z_{1}^{3} \qquad 2M \qquad E = Y_{2}Z_{1} \qquad IM$$

$$F = D + E \qquad F = D + E$$

$$G = Z_{1}C \qquad IM \qquad G = C + F$$

$$H = FX_{2} + GY_{2} \qquad 2M \qquad H = Z_{1}Z_{2} \qquad IM$$

$$Z_{3} = GZ_{2} \qquad IM \qquad I = C^{3} + aHC^{2} + HFG \qquad 6M$$

$$I = F + Z_{3} \qquad X_{3} = aZ_{3}^{2} + IF + C^{3} \qquad 5M \qquad Z_{3} = HC^{3} \qquad IM$$

$$Y_{3} = IX_{3} + HG^{2} \qquad 3M \qquad Y_{3} = GI + C^{2}[FX_{1} + CY_{1}] \qquad 5M$$

$$-----$$

$$20 M$$

Similarly, the two forms of formulas for projective point doubling are shown below:

$$P = (X_1, Y_1, Z_1); P + P = (X_3, Y_3, Z_3)$$

$(x, y) = (X/Z^2, Y/Z^3) \rightarrow (X, Y, Z)$

$$(x, y) = (X/Z, Y/Z) \rightarrow (X, Y, Z)$$

$$Z_3 = X_1 Z_1^2 \qquad 2M \qquad A = X_1 Z_1 \qquad IM$$

$$A = bZ_1^2 \qquad IM \qquad B = bZ_1^4 + X_1^4 \qquad 5M$$

$$B = X_1 + A \qquad \qquad C = AX_1^4 \qquad IM$$

$$X_3 = B^4 \qquad 2M \qquad D = Y_1 Z_1 \qquad IM$$

$$C = Z_1 Y_1 \qquad IM \qquad E = X_1^2 + D + A$$

$$D = Z_3 + X_1^2 + C \qquad IM \qquad Z_3 = A^3 \qquad 2M$$

$$E = DX_3 \qquad IM \qquad X_3 = AB \qquad IM$$

$$Y_3 = X_1^4 Z_3 + E \qquad 2M \qquad Y_3 = C + BE \qquad IM$$

$$\frac{---}{10M} \qquad 12M$$

The squaring calculation over  $GF(2^k)$  is assumed very similar to the multiplication computation. They are both denoted as M (multiplication) in the above. Since the number of additions is taken to be, on the average, half the number of bits, it can be clearly seen from the above tables that the projective coordinate  $(x, y) = (X/Z^2, Y/Z^3)$  has on the average 20 multiplication iteration, while the projection (x, y) = (X/Z, Y/Z) has on the average 20.5 multiplications. Clearly, the former would be the projection of choice for sequential implementation. However, as will be discussed later, the projection (x, y) = (X/Z, Y/Z) has an advantage for parallel implementation.

#### 2.4. Remarks

As can be observed from before, the number of multiplication processes for adding and doubling two EC points in GF(p) is found to be different than  $GF(2^k)$ . Furthermore, this number is different depending on the specific procedure used in the field, i. e., (X/Z, Y/Z) or  $(X/Z^2, Y/Z^3)$ . Comparison of the number of operations to chose the proper finite field is not accurate because operations in GF(p) require completely different calculation time than  $GF(2^k)$ .

The following section will implement two modulo multiplication hardware for both fields GF(p) and  $GF(2^k)$ . The two hardware designs will be compared depending on speed and area to compute ECC arithmetic computations.

# 3. Modular Multiplication Hardware

The straightforward approach to compute modular multiplication is by performing multiplication followed by reduction [21, 22]. The multiplication can be computed through several addition operations. Then, the reduction is performed through several subtractions, by subtracting the modulus several times until the result is less than the modulus. This approach is inefficient and suffers from very low speed. It can, however, be improved by merging modulo subtraction with the multiplication-add operations [7], as Algorithm 1.

```

Algorithm 1:

Define k: Number of bits in x; x_i: The i^{th} bit of x

Input: x, y, and n; where x, y < n;

Output: P = xv \mod n

```

```

1. P := 0:

2. For i = k - 1 down to 0;

3. {

4

P := 2P:

5.

If P \ge n then

P := P - n;

6.

If x_i = 1 then {

7.

P := P + y;

8.

If P \ge n then

P := P - n

9.

10. End;

```

Algorithm 1 is developed for GF(p). In order to use this algorithm for  $GF(2^k)$ , the carry propagation is not needed any more. All the addition and subtraction operations are replaced by exclusive-OR (XOR) computations. The 'if' statement in step 8 of Algorithm 1 is not required, because the result of XOR-ing P with y cannot be more than the modulus. Algorithm 1 can be modified to be used for  $GF(2^k)$  as shown in Algorithm 2.

Algorithm 2:

```

Define k: Number of bits in x; x_i: The i^{th} bit of x

Input: x, y, and f(x); where x, y, f(x) \in GF(2^k)

Output: P = xy \mod f(x)

1. P := 0;

2. For i = k - 1 down to 0;

3. {

4. P := 2P;

5. If P_k = 1 then

P := P \oplus f(x);

6. If x_i = 1 then

P := P \oplus y;

7. }

8. End;

```

These two algorithms are implemented in hardware in the following subsections. The purpose of the implementations is for proper multiplication comparison between GF(p) and  $GF(2^k)$  finite fields.

#### 3.1. GF(p) Modular Multiplication Hardware

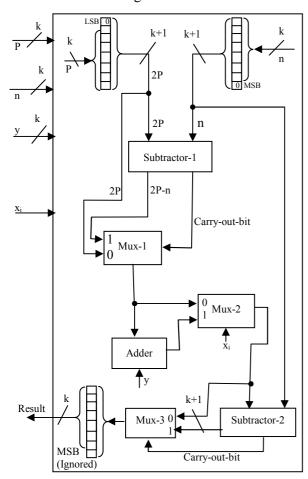

Algorithm 1 for GF(p) modulo multiplication is found to be very suitable for VLSI implementation [7]. It has a bounding 'for' loop, which includes iterative modulo multiplication reduction operations. The bounding loop can be designed in hardware as a controller that will control the number and processes of the iterations. The modulo multiplication reduction is implemented in hardware with three adders and three multiplexors connected as shown in Figure 1. There are no registers in the design, the small boxes shown are only to show the correct mapping of bit-flow. The adder can function as a subtractor if one of its inputs is inverted. The complete process of  $x.y \mod n$  will need k clock cycles,

if each modulo reduction iteration is performed in one clock cycle. The multiplication of P by two (as in step 4 of Algorithm 1) is performed by a shift to the bits of P toward the left. The multiplexors: Mux-1, and Mux-3, are controlled by the subtractor's output-carry bit. Therefore, the complete subtractions are to be made for the Mux to give the output. Assume k is the number of bits we are working with. The simplest adder, carry ripple adder, is constructed from k - 1 Full Adders (FA) and one Half Adder (HA) [19, 23]. Each FA is built of two XOR gates, two AND gates, and one OR gate [19]. The HA is constructed of an XOR gate, and an AND gate. The subtractor is different than the adder with the addition of k NOT gates. If we use the NOT gate as our gate reference, as described in [5], each XOR gate is equivalent to three gates, and each AND and OR gate is the same as two gates [5]. The Adder's area will be equivalent to 12k - 7 gates. The subtractor will have an area similar to 13k - 7 gates.

Figure 1. *GF(p)* modulo reduction hardware.

Each multiplexor is made of 2k AND gates, k OR gates and one NOT gate [23]. The area of the multiplexor is equivalent to 6k + 1 NOT gates. The complete hardware shown in Figure 1 is constructed of the following gates: (6k - 3) XOR + (12k - 3) AND + (6k - 3) OR + (2k + 3) NOT, which is equivalent to 56k - 18 NOT gates. For the reason of comparison, assume the delay is constant for different gates. The longest path in the adder and the subtractor is found to be

through 2k gates, because of the carry propagation. The multiplexor's delay is through three gates. The complete GF(p) hardware longest path is found to be through three adders and three multeplexors, which made it to be through 6k + 9 gates.

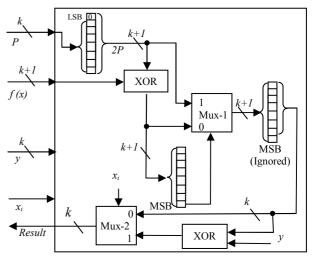

# 3.2. GF(2<sup>k</sup>) Modular Multiplication Hardware

Algorithm 2, is a modification of Algorithm 1 to make it suitable for  $GF(2^k)$ . It has a similar bounding 'for' loop the same as Algorithm 1, which make the controller of  $GF(2^k)$  the same as GF(p). The  $GF(2^k)$  modulo multiplication reduction hardware is shown in Figure 2. It requires only two multiplexors and two k-parallel XOR gates. Mux-1 and Mux-2 are to perform the 'if' comparisons of step 5 and 6 in Algorithm 2. The number of gates used in this hardware is  $2k \ XOR + 4k \ AND + 2k \ OR + 2 \ NOT$ , which is equivalent to 18k - 2 NOT gates.

Figure 2. GF(2k) modulo reduction hardware.

As mentioned before, the addition operation of GF(p) is replaced by bit-wise XOR-ing which does not have any carry propagation. This made the area and speed of  $GF(2^k)$  multiplication more practical to be used. Referring to the same assumption of constant delay for different gates, the longest path for the  $GF(2^k)$  hardware shown in Figure 2 is found to be of only 7 gates.

More elaboration on the hardware shown in Figure 2 is performed to make it modified to be even faster. This modified design is shown in Figure 3. Its speed is accomplished with the cost of some more hardware area. The longest path is made shorter and is found to be through only 4 gates instead of 7. This modified scheme requires three k-parallel XOR gates and a 4×1-multiplexor. The 4×1-multiplexor, as mentioned in [19], is made up of 4k AND + k OR + 2 NOT gates. The  $GF(2^k)$  modified hardware area is found to be equivalent to 19k + 2 NOT gates.

Figure 3. Modified  $GF(2^k)$  modulo reduction hardware.

#### 3.3. Discussion

In order to compare the different hardware designs described before, their areas and delays are listed in Table 3. The table is expressed into the number of bits 'k' used. Note that the multiplication in  $GF(2^k)$  requires a fixed amount of time. While multiplication in GF(p) depends on the number of bits used. If the numbers, for example, are expressed into 300-bits, the longest path in GF(p) is found to be through 1809 gates. This long path makes the design very slow when compared to the fixed longest path of  $GF(2^k)$ . The hardware area of GF(p) is found to be around three times larger than  $GF(2^k)$ .

Table 3. Comparing the three multipliers.

| Modulo Multiplication<br>Hardware Design | Area (Equivalent to NOT Gates) | Delay (Longest<br>Path # Gates) |

|------------------------------------------|--------------------------------|---------------------------------|

| GF(p) (Figure 1)                         | 56k - 18                       | 6k + 9                          |

| GF(2 <sup>k</sup> ) (Figure 2)           | 18k - 2                        | 7                               |

| GF(2 <sup>k</sup> ) (Figure 3)           | 19k + 2                        | 4                               |

The main problem of GF(p) hardware designs, compared with  $GF(2^k)$ , is due to the carry propagation issue. This problem have been tried out to be solved by several methods. However, none of theses techniques can have the speed nor the area of  $GF(2^k)$  [19]. These reasons made the motivation to choose working with  $GF(2^k)$  instead of GF(p) for ECC hardware design.

# 3.4. Different Implementations of Algorithm 2

Referring to Algorithm 2 for  $GF(2^k)$  multiplication, the loop can be unfolded differently to design different multipliers. It can use any of the two modules of the modulo reduction designs shown in Figures 2 or 3. The area difference between the designs of Figure 2 and 3 is not much, Figure 3 is 5% larger than Figure 2. However, the speed of the hardware shown in Figure 3 is 43% faster than the one shown in Figure 2. The

speed difference makes the choice of the hardware of Figure 3 to be the practical module to be used.

Algorithm 2 can be unfolded and implemented in several ways. A fully parallel way, where the number of reduction modules is the same as the number of bits, is described in the next subsection. Partially parallel methods will be introduced later.

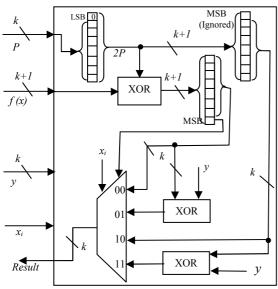

### 3.4.1. Fully Parallel Hardware

Completely unfolding Algorithm 2 will give a fully parallel modulo multiplier. It is assumed that it performs its computation in one clock cycle. This parallel hardware is shown in Figure 4.

Figure 4. Unfolded  $GF(2^k)$  parallel multiplier.

This  $GF(2^k)$  parallel multiplier is made of four registers and k-modulo reduction modules, assuming k is the number of bits of x and y. All registers are for holding k-bits except one, which is for f(x), holding k+1 bits. The register holding the value of x is mapping each bit to a different modulo reduction unit. The registers holding the bits of y and f(x) broadcast their bits to all modulo reduction modules. The longest path in this  $GF(2^k)$  parallel multiplier is found to be through 4k gates. This longest path will define the length of the clock cycle needed.

The area of this design includes the register's area. The k-bit register is constructed of k D-Flip-Flops (DFF), where each DFF is made of six NAND gates as described in [11]. This makes all four registers to be made of 24k + 6 NAND gates. Each NAND gate is equivalent to a NOT gate [23], which makes the registers area of 24k + 6 NOT gates. All the modulo reduction hardware area is equivalent to  $19k^2 + 2k$ NOT gates. The complete  $GF(2^k)$  fully parallel multiplier hardware is found to have an area equivalent to  $19k^2 + 26k + 6$  NOT gates. This area is very huge to implement. In order design to

implementation, a partially parallel hardware is developed.

#### 3.4.2. Partially Parallel Hardware

The data flow graph shown in Figure 4 can be implemented in hardware in several ways, depending on the size of the hardware to be implemented. For example, if the area available for the modular multiplier is equivalent to 50k NOT gates, only two reduction units can fit in this area. This means that this hardware will need k/2 clock cycles to complete a modulo multiplication process. For this research, the ECC coprocessor is investigated, and depending on it, the proper partial parallel hardware is designed.

## 4. ECC Coprocessor

The  $GF(2^k)$  partially parallel modular multiplier described before is used as the basic unit in an ECC coprocessor. Assume P is an elliptic curve point used for ECC. The ECC algorithm used for calculating nP from P is the binary method, since it is known to be efficient and practical to implement in hardware [2, 4, 10, 21, 22]. This binary method algorithm is shown below as Algorithm 3.

Algorithm 3:

Define k: Number of bits in n;  $n_i$ : The i<sup>th</sup> bit of n Input: P (a point on the elliptic curve). Output: Q = nP (another point on the elliptic curve).

```

If n<sub>k-1</sub> = 1, then Q := P;

Else Q := 0;

For i = k - 2 down to 0;

{

Q := Q + Q;

4. If n<sub>i</sub> = 1 then

Q := Q + P;}

Return O;

```

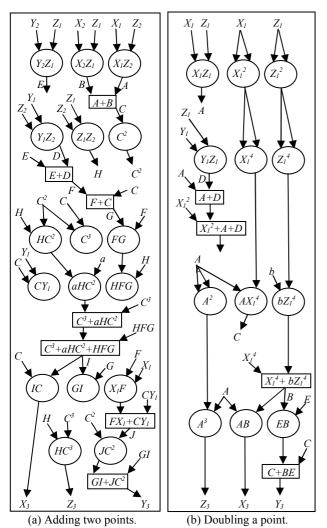

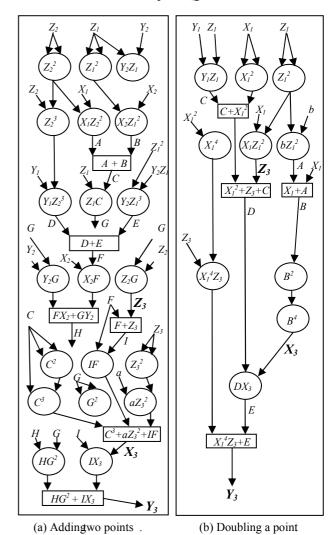

The binary method algorithm scans the binary bits of n and doubles the point Q, k - times. Whenever, a particular bit of n is found to be one, an extra operation is needed. This extra operation is Q + P. Adding two elliptic curve points and doubling a point are to be performed in the projective coordinates system to avoid the inversion operation. The data flow graph for EC point operations are shown in Figure 5 for projecting (x, y) to (X / Z, Y / Z), and shown in Figure 6 for the projection to  $(X / Z^2, Y / Z^3)$ . Both Figures 5 and 6 shows the dependency between the data values which defines possible designing method using three parallel  $GF(2^k)$  multipliers.

It is found to be unpractical to fully implement the elliptic curve point operations as shown in the Figures 5 or 6 for the different  $GF(2^k)$  projective coordinate procedure forms. The area of both figures is very large and the clock cycle will be inefficient. This made the

idea of designing hardware models with a less number of small multipliers more suitable to do as will be clarified in the following subsections.

Comparing the two projective forms, projecting (x, y) to  $(X / Z^2, Y / Z^3)$  requires, on the average, less number of multiplications than projecting into (X / Z, Y / Z) as shown in Table 4. Although, the later uses three less multiplication operations in adding two different elliptic points, it uses two more multiplication operations in doubling an elliptic point. It is worth remembering that the number of doubling is usually more than the number of additions. Since, the projection  $(X / Z^2, Y / Z^3)$  requires less number of multiplications, it is more suitable for sequential implementation, i.e. when using a single multiplier, as has been reported in the literature.

For (x, y) = (X/Z, Y/Z), the minimum computation time to perform one elliptic point operation in the calculation of nP is, on the average,  $7 GF(2^k)$ multiplications when using three multipliers. When using the projection of  $(X/Z^2, Y/Z^3)$  as in Figure 6, this time is, on the average, 8.5  $GF(2^k)$  multiplications. Furthermore, the utilization of the three multipliers in Figure 5 is much higher than that in Figure 6. As can be seen in Figure 5, all the three multipliers will be used in all of the steps except one. While in Figure 6, there are idle multipliers in four multiplication steps. This clearly indicates that the parallel implementation of projective coordinate (X / Z, Y / Z) requires less number of cycles and hence it is faster than projecting (x, y) to  $(X/Z^2, Y/Z^3)$ , and should be the projection of choice for our architecture. This is contrary to sequential implementation.

# **4.1. General Elliptic Curve Point Operation Hardware**

Reconsider Algorithm 3 described before, the two operations to be repeated for *k-iterations* are doubling an elliptic curve point and adding a point to another. It is found that they cannot be performed in parallel (each of these computations is to be performed separately). This made the idea of designing a general point operation hardware.

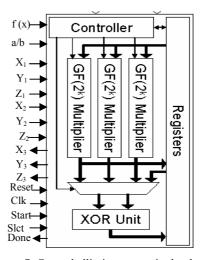

The general elliptic curve point operation hardware is outlined in Figure 7. It is informed about the type of computation to be done through a signal 'Slct'. If 'Slct' is high, the hardware is to do an elliptic curve doubling operation. If 'Slct' is low, the hardware is to do addition of two elliptic curve points. The hardware begins its operation when 'Start' signal is raised. The 'Start' signal also indicates to the hardware that all the input data values are available so the controller will command the registers to load them. The controller will then command the data flow to be routed to perform the proper elliptic curve computation. When the computation is complete, a 'Done' flag is raised indicating that the results are ready at the data output

pins. The controller guides the hardware to perform one of the two operations, each at its appropriate time. The routing of data is performed through multiplexors to direct the data flow between the registers and the multipliers and XOR operation module. The controller is to influence the multiplexors selection signal and the registers loading signal.

Figure 5. Data flow graphs for the elliptic curve point operations of projecting (x, y) to (X/Z, Y/Z).

Table 4. Comparison between the different designs.

| Projecting (x, y) to | Number of<br>Multipliers | Avg. # of<br>Multiplication Cycles |

|----------------------|--------------------------|------------------------------------|

| $(X/Z^2, Y/Z^3)$     | 1                        | 20                                 |

|                      | 3                        | 8.5                                |

|                      | 1                        | 20.5                               |

| (X/Z,Y/Z)            | 3                        | 7                                  |

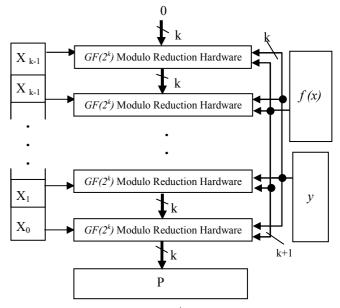

### 4.2. ECC Coprocessor

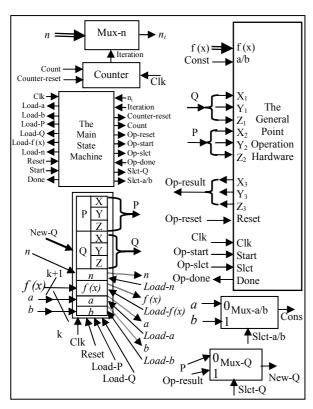

Algorithm 3 is the main procedure to be implemented in hardware for designing the ECC coprocessor. This hardware requires nine k-bit registers and one k + 1 bit register for storing the modulus f(x). Three of the nine are for holding the projective coordinates of the original elliptic curve point P(X, Y, Z). Another three k-bit registers are for keeping the constants n, a, and b.

The three remaining registers are for storing the intermediate values of the point Q.

Figure 6. Data flow graphs for the elliptic curve point operations of projecting (x, y) to  $(X/Z^2, Y/Z^3)$ .

Figure 7. General elliptic curve point hardware outline.

The ECC coprocessor hardware is shown in Figure 8. It contains, other than the registers, three multiplexors, a counter, a state-machine, and the general point operation hardware. The three multiplexors are Mux-Q, Mux-a/b, and Mux-n. Mux-Q

and Mux-a/b are two similar multiplexors. Their function is to choose one of two input buses to connect to their outputs depending on their select signals. Mux-n, however, will choose a bit  $n_i$  from the k-bits of n. The selection of this  $n_i$  depends on the counter's output value named 'Iteration'. For example, if iteration value is 0, the output of Mux-n will be the most significant bit of n ( $n_{k-1}$ ). If 'Iteration' value is k - 1, the outcome of Mux-n will be the least significant bit of n ( $n_0$ ). Iteration k - 1 also indicates that the computation is about to produce its final result.

Figure 8. Proposed ECC coprocessor hardware.

The computations are performed in the general point operation hardware. This hardware is described before and detailed in Figure 8. The hardware depends on the signal 'Op-slct' to either double a point or to perform a point addition operation. When the operation hardware computation is completed, a signal 'Op-done' is raised. The multiplexors, counter, registers, and general point operation hardware, are all controlled by the main state machine. This state machine resets its states at the beginning. Then, it loads all the input data values, then, the state machine checks if the most significant bit of *n*  $(n_{k-1})$  has the value one it loads P into register Q. If not, register Q keeps its original values of zeros. Then, the elliptic curve point operations begin. It starts with iteration number 1 and proceed until iteration k-1. Iteration k-l is the last one to process, where the result should be ready after it.

#### 4.3. Area Flexibility

The ECC coprocessor is designed to deal with numbers that are in the order of k-bits. However, The size of the

hardware can be designed depending on the area available. In other words, the ECC coprocessor is built of two types of components, fixed size modules and flexible size ones. All modules are fixed size ones except the multiplier, which is completely flexible to the area available. Depending on the area available the number of modulo multiplication reduction modules are chosen. This flexible size multiplier is described in depth before.

#### 5. Conclusion

We modified a GF(p) multiplication algorithm to make suitable for  $GF(2^k)$ . Then, both multiplication algorithms where modeled as hardware designs to compare them thoroughly. The modified  $GF(2^k)$  algorithm showed fixed fast speed and smaller area relative to the GF(p) multiplier. A further hardware improvement have been accomplished to the  $GF(2^k)$  multiplier to make it faster. This improvement gained more than 40% in speed with an area cost of 5%.

The  $GF(2^k)$  multiplier was used to build a complete ECC coprocessor. The point operation was processed in a projective coordinate manner to avoid the lengthy inversion computation. In fact, the inversion is needed only at the beginning and at the end, two times only, which made the assumption to compute it in software. This design is attractive because of its simplicity and suitability to be implemented in VLSI with today's technology.

### **Acknowledgements**

Thanks to KFUPM, Saudi Arabia, for all the support they are giving to conduct research.

#### References

- [1] Al-Daoud E., and Ramlan M., "A New Addition Formula for Elliptic Curves Over GF(2n)," *IEEE Transactions on Computers*, vol. 51, no. 8, August 2001.

- [2] Blake, Seroussi, and Smart, *Elliptic Curves in Cryptography*, Cambridge University Press, NY, 1999

- [3] Chung J. W., Sim S. G., and Lee P. J., "Fast Implementation of Elliptic Curve Defined Over GF(pm) on CalmRISC with MAC2424 Coprocessor," in Proceedings of Workshop on Cryptographic Hardware and Embedded Systems (CHES'2000), August 2000.

- [4] Crutchley D. A., "Cryptography and Elliptic Curves," *MS Thesis*, Faculty of Math, University of Southampton, England, May 1999.

- [5] Ercegovac M. D., Lang T., and Moreno J. H., Introduction to Digital System, John Wiley & Sons, New York, 1999.

- [6] Ernst M., Klupsch S., Hauck O., and Huss S. A., "Rapid Proto-Typing for Hardware Accelerated Elliptic Curve Public-Key Cryptosystems," in Proceedings of the IEEE 12<sup>th</sup> International Workshop on Rapid System Prototyping, Monterey, CL, June 2001.

- [7] Gutub A. and Tenca, "Efficient Scalable VLSI Architecture for Montgomery Inversion in GF(p)," VLSI Journal, vol. 37, no. 2, 2004.

- [8] Gutub A., "Fast Elliptic Curve Cryptographic Processor Architecture Based on Three Parallel GF(2k) Bit Level Pipelined Digit Serial Multipliers," in Proceedings of the IEEE 10<sup>th</sup> International Conference on Electronics, Circuits and Systems (ICECS'2003), UAE, pp. 72-75, December 2003.

- [9] Gutub A., "VLSI Core Architecture for GF(P) Elliptic Curve Crypto Processor," in Proceedings of the IEEE 10<sup>th</sup> International Conference on Electronics, Circuits and Systems (ICECS'2003), UAE, pp. 84-87, December 2003.

- [10] Hankerson D., Hernandez J. L., and Menezes A., "Software Implementation of Elliptic Curve Cryptography Over Binary Fields," in Proceedings of Workshop on Cryptographic Hardware and Embedded Systems (CHES'2000), August 2000.

- [11] López J., and Dahab R., "High-Speed Software Multiplication in GF(2m)," *IC 00-09 Technical Report*, Inst. Comp., University of Campinas, May 2000.

- [12] Miyaji A., "Elliptic Curves Over F<sub>P</sub> Suitable for Cryptosystems," *in Proceedings of the Advances in Cryptology- AUSCRUPT'92*, Australia, December 1992.

- [13] Moon S., "A 193-bit Encryption Processor for Elliptic Curve Cryptosystem Using Fast VLSI Algorithms in Finite Fields," in Proceedings of the IEEE Consumer Communications and Networking (CCNC'2005), pp. 611-613, January 2005.

- [14] Okada S., Torii N., Itoh K., and Takenaka M., "Implementation of Elliptic Curve Cryptographic Coprocessor Over GF(2m) on an FPGA," in Proceedings of Workshop on Cryptographic Hardware and Embedded Systems (CHES'2000), August 2000.

- [15] Orlando G., and Paar C., "A High-Performance Reconfigurable Elliptic Curve Processor for GF(2m)," in Proceedings of Workshop on Crptographic Hardware and Embedded Systems (CHES'2000), August 2000.

- [16] Orton J. A., Roy M. P., Scott P. A., Peppard L. E., and Tavares S. E., "VLSI Implementation of Public-Key Encryption Algorithms," in Proceedings of the Advances in Cryptology (CRYPTO'86), August 1986.

- [17] Paar C., Fleischmann P., and Soria-Rodriguez P., "Fast Arithmetic for Public-Key Algorithms in Galois Fields with Composite Exponents," *IEEE Transactions on Computers*, vol. 48, no. 10, October 1999.

- [18] Saqib N. A., Rodriguez-Henriquez F., and Diaz-Perez A., "A Parallel Architecture for Computing Scalar Multiplication on Hessian Elliptic Curves," in Proceedings of the IEEE International Conference on Information Technology: Coding and Computing (ITCC'04), vol. 2, pp. 493-497, 2004.

- [19] Saqib N. A., Rodriguez-Henriquez F., and Diaz-Perez A., "A Parallel Architecture for Fast Computation of Elliptic Curve Scalar Multiplication over GF(2m)," in Proceedings of the IEEE 18<sup>th</sup> International Parallel and Distributed Processing Symposium (IPDPS'04), pp. 144, April 2004.

- [20] Scott N. R., Computer Number Systems and Arithmetic, Prentice-Hall, New Jersey, 1985.

- [21] Stallings W., Cryptography and Network Security: Principles and Practice, Prentice Hall Inc., NJ, 1999.

- [22] Stinson D. R., *Cryptography: Theory and Practice*, CRC Press, Boca Raton, Florida, 1995.

- [23] Tocci R., and Widmer N., *Digital Systems: Principles and Applications*, Prentice-Hall, New Jersey, 2001.

Adnan Abdul-Aziz Gutub is a faculty member in the Computer Engineering Department at King Fahd University of Petroleum and Minerals (KFUPM), Saudi Arabia. He received his BSc degree in

electrical engineering in 1995, his MSc degree in computer engineering in 1998 both from King Fahd University of Petroleum and Minerals, and his PhD degree in 2002 from the Department of Electrical and Computer Engineering at Oregon State University in cryptographic hardware design. His research interests include modeling, simulating, and synthesizing VLSI hardware for computer arithmetic operations. He worked on designing efficient integrated circuits for the Montgomery inverse computation in different finite fields. He has been awarded the visiting internship for 2 months of summer 2005 sponsored by British Council at Brunel University to collaborate with Bio-Inspired Intelligent System (BIIS) research group in a project to speed-up a scalable modular inversion hardware architecture.